CoaXPressカメラをFPGAで動かしてみた

ミラクシアエッジテクノロジーの平岡です。 ミラクシアでは組込みソフトウェア設計サービスや基板設計サービス、FPGA(Field Programmable Gate Array)を活用したデジタル回路設計サービスを提供しています。

特に、FPGAを取り扱う開発では高速カメラの出力を受ける環境構築や、カメラから出力される画像を低遅延で処理するデジタル回路の開発に注力しています。 本記事では、FPGA上にCoaXPressカメラを制御するHOST-IPを搭載し、カメラ画像を取得する方法についてご紹介します。

CoaXPressカメラとFPGAの概要

CoaXPressカメラは、主に産業用画像処理の分野で活用されている高性能カメラです。 代表的な特徴は次の通りです。

・大容量・高速データ転送:1レーン当たり最大12.5Gbpsの転送帯域を有する。

・長距離伝送:長距離(数十m~100m以上)でも性能維持。

・システム設計の容易さ:同軸ケーブルのみで映像・制御・電源すべてを対応可能。

・堅牢性・信頼性:ノイズ耐性、堅牢な物理コネクタで、過酷な産業現場でも安心。

・拡張性:画像伝送のレーン数を増やせば、さらに高帯域のシステムも構築可能。

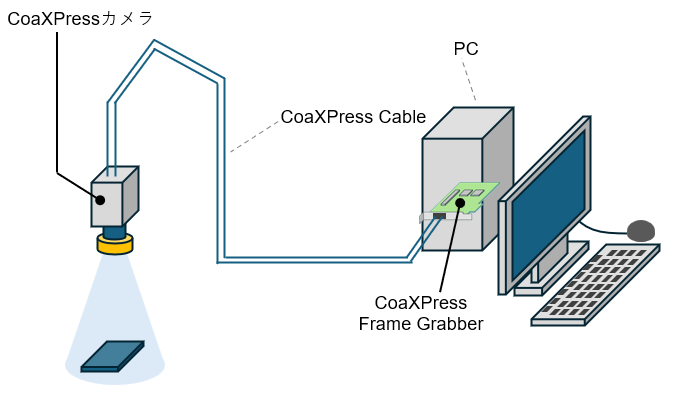

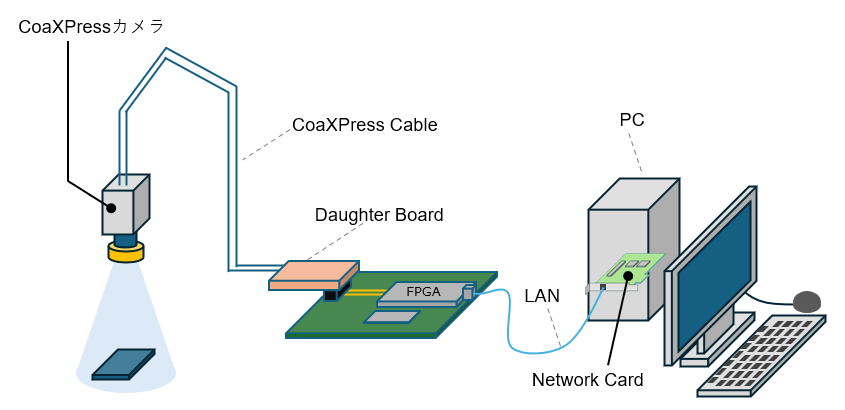

一般的には、CoaXPressカメラからの画像データは「Frame Grabber」と呼ばれる専用ボードを用いて、図1-1のような構成でPCに取り込むことが多いです。

本記事では、Frame Grabberを使わず、FPGAを利用してCoaXPressカメラの画像データを直接受信するシステムの開発事例についてご紹介します。

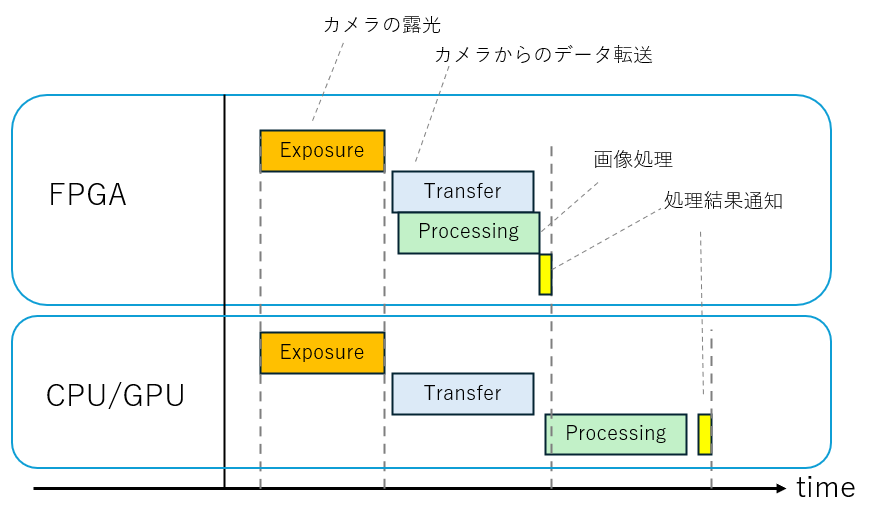

FPGAはリアルタイムで並列処理を行えるため、カメラから受信した画像をそのまま高速に処理することが可能です。そのため、FPGAを用いた構成では従来のCPUやGPUによる画像処理システムと比較して、図1-2のように全体のスループットや応答速度を大きく向上できるというメリットがあります。

このようなFPGAベースのシステム設計に挑戦した事例について、次章で解説します。

図1-1 CoaXPressカメラとPC接続構成例

図1-2 FPGAとCPU/GPUでの画像処理時間イメージ

システム構成と開発機器

全体構成(FPGA+カメラ+PCや周辺機器)を図2-1に示します。 FPGAを用いた構成では、CoaXPressカメラの出力は、CoaXPress用のDaughterBoardを経由してFPGAに入力します。 Daughter Board上にはカメラからのDownLink信号(CoaXPressカメラ→FPGA)とUpLink信号(FPGA→CoaXPressカメラ)とCoaXPressカメラへの電源供給信号を同軸にするMicroBNCコネクタと同軸ケーブルを通した高速信号の劣化を補正し、伝送品質を確保するためのEqualizerチップが搭載されています。

図2-1 CoaXPressカメラとFPGA/PCとの接続構成例

FPGA内のロジック構成

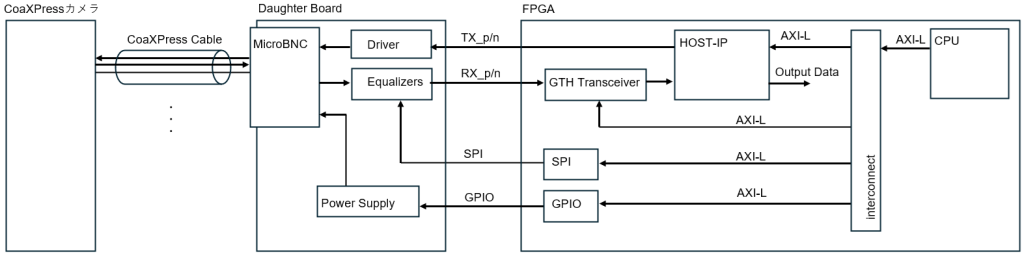

今回使用するFPGAはAMD Zynq UltraScale+ MPSoC Evaluation Kit を用いており、ロジック内には高速シリアル信号を受信するGTH Transceiver IP、CoaXPressプロトコルの復号するために3rdパーティのCoaXPress IP Core Host、それ以外にDaughter Board上のIC制御のためのSPI-IPと電源供給PoCXPenのON/OFF制御ためのGPIO-IPを組み込んでいます。FPGAのIP構成とDaughter Boardとの接続関係を図3-1に示します。

FPGAが行う制御経路は4系統あり、各制御内容を以下に示します。 ①HOST-IPの制御 CoaXPressカメラへの各種設定やHOST自体の制御・レジスタ設定が必要です。

②GTH Transceiver IPの制御 CoaXPressカメラから伝送されたシリアルデータ信号を復調するために予めシリアルデータ信号の伝送周波数に対応したパラメータ設定をGTH Transceiver IPに行う必要があります。 なお、GTH Transceiver IPを経由するのはDownLink信号(RX_ p/nの信号)のみです。UpLink信号は速い転送速度でも41.6MbpsのためGTH Transceiver IPを経由しません。

③Daughter Board上のEqualizer ICの制御 ②と同様にCoaXPressカメラから伝送されたシリアルデータ信号を信号補償・整形するために、シリアルデータ信号の伝送周波数に対応したレジスタ設定をEqualizer ICに行う必要があります。

④Daughter Board上のPower Supply の制御 CoaXPressカメラの電源はCoaXPress Cableを経由して供給されるためPowerON/OFFの制御をGPIOで行う必要があります。

図3-1 FPGAのIP構成

カメラ画像の取得手順

CoaXPressカメラにはBootstrapレジスタというレジスタ群が備えられています。Bootstrapレジスタは、CoaXPress規格で定義されている基本機能を制御・監視するための標準的なレジスタ群です。 基本的にはBootstrapレジスタ内のレジスタに設定を行うことでCoaXPressカメラを制御していきます。

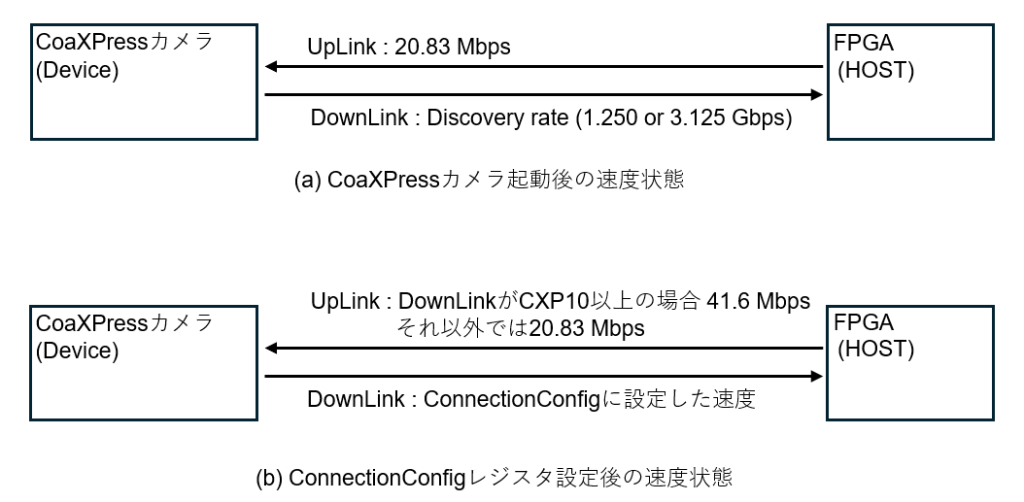

また、CoaXPressカメラは、図4‐1のように起動時はDiscovery rateというCoaXPress規格で定められた通信速度で起動します。そのため起動後にFPGA側からCoaXPressカメラの Bootstrapレジスタ内のConnectionConfigレジスタに、実際に動かしたい速度設定を行うことで通信速度を切り替える手順で動作させることになります。

図4‐1 通信速度状態

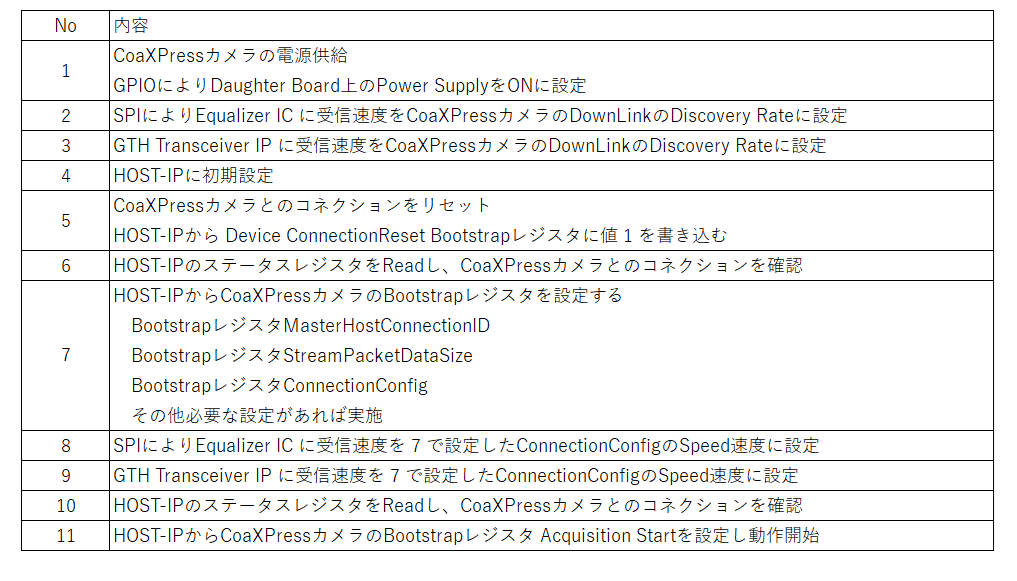

表4-1 制御手順

■起動後のコネクション 表4-1のNo2・No3では、GTH Transceiver IP とDaughter Board上のEqualizer IC に対して、CoaXPressカメラのDownLinkのDiscovery rateの速度を設定する必要があります。CoaXPress規格Version2.1ではHigh Speed(DownLink)のDiscovery rateは2つあります。使用しているCoaXPressカメラのDiscovery rateがどちらをサポートしているか不明な場合は2通りの速度でNo2~6を実施すればよいです。

■起動後の設定 起動後にCoaXPressカメラとの接続が確立したら表4-1のNo7の工程でCoaXPressカメラに設定すべき以下の設定を行います。

・MasterHostConnectionIDレジスタの設定 接続されているCoaXPressカメラが、どの接続先HOST(FPGA)通信しているかを示すID値です。HOST-IPは仕様によってはデータ内のIDを見分けているケースがあるため、HOST-IPにID値を設定している場合はその値と合わせる必要があります。

・StreamPacketDataSizeレジスタの設定 CoaXPressカメラが一度に連続して送信してよい最大のStream(画像)データサイズを指定するレジスタです。FPGAのHOST-IPは受けれるデータサイズが決まっていますので、それ以下のサイズにしておく必要があります。

・ConnectionConfigレジスタの設定 CoaXPressカメラとFPGA(規格ではHOST)との接続設定を行うレジスタです。 CoaXPressカメラとのコネクション数(物理的に接続しているケーブル数)と転送速度の2つがConnectionConfigレジスタにアサインされています。なお、速度の設定値はCoaXPress規格で定められています。

■速度変更後に再度コネクション 表4-1のNo8~10の手順では、GTH Transceiver IP とDaughter Board上のEqualizer IC に対して、表4-1のNo7でConnectionConfigレジスタに設定した通信速度に設定しなおします。 これにより、FPGA側で速度変更後のDownLinkを受信することができます。

■カメラの撮像開始 表4-1のNo11の手順ではCoaXPressカメラのAcquisitionStartレジスタを設定してカメラを動作開始させます。もし、CoaXPressカメラを同期設定で動作させたいなど設定変更する場合はAcquisitionStartレジスタの設定前に実施してください。

以上の手順でCoaXPressカメラが撮像を開始し、FPGAのHOST-IPでカメラの出力する画像を受信することができます。

まとめ

本稿では、FPGAにCoaXPressカメラを制御するHOST-IPを搭載し、カメラ画像を取得するまでの流れをご紹介しました。 画像処理分野では、画像の高解像度化によって処理精度などの性能向上が期待できるため、より高解像度かつ高速インターフェースに対応したCoaXPressカメラをFPGAに接続するケースが増えています。 本稿の内容が、CoaXPressカメラを取り扱う開発や課題解決の一助となれば幸いです。

採用情報

ミラクシアでは一緒に組込みソフト開発をする仲間を募集しています。