LVDSデータデシリアライザIPのベンダ置き換え事例紹介

1.序文

初めまして、ミラクシアエッジテクノロジーの須田です。 本ブログでは、他社FPGAへの置き換えに伴うIP置き換えに際して、設計者がつまずきやすいポイントと、その解決アプローチをLVDSデータデシリアライザIPを例としてご紹介します。

特に、

- LVDSデシリアライザIPの仕様差分はどこを比較すればよいか分からない

- 入力可能なch数が置き換え前後で異なっており、困っている

- 設定可能なシリアライズ係数が異なるため置き換えできない

- データ遅延量の分解能の差が、動作にどう効くかイメージしづらい

といった方を想定し、A社FPGA → B社FPGAへの置き換え事例を通じて、検討の勘所を整理します。

2.LVDSデシリアライザIP置き換えでつまずきがちなポイント

2-1.仕様比較で必ず確認すべき項目

デシリアライザIP置き換え検討において、カタログスペックとして比較する必要のある項目は以下表1となります。

表1 カタログスペック比較表

| 項目 | 内容 |

|---|---|

| 入力データch数 | IPに入力可能な差動データペア数 |

| 最大データレート | シリアルデータの上限速度 |

| データレートモード | Single Data Rate(SDR)もしくはDouble Data Rate(DDR) |

| シリアライズ係数 | 1本のシリアル入力を何ビット幅まで展開可能か |

| データ遅延量の分解能と最大値 | クロックエッジに対してデータを遅延させる際、その最小単位と最大値 |

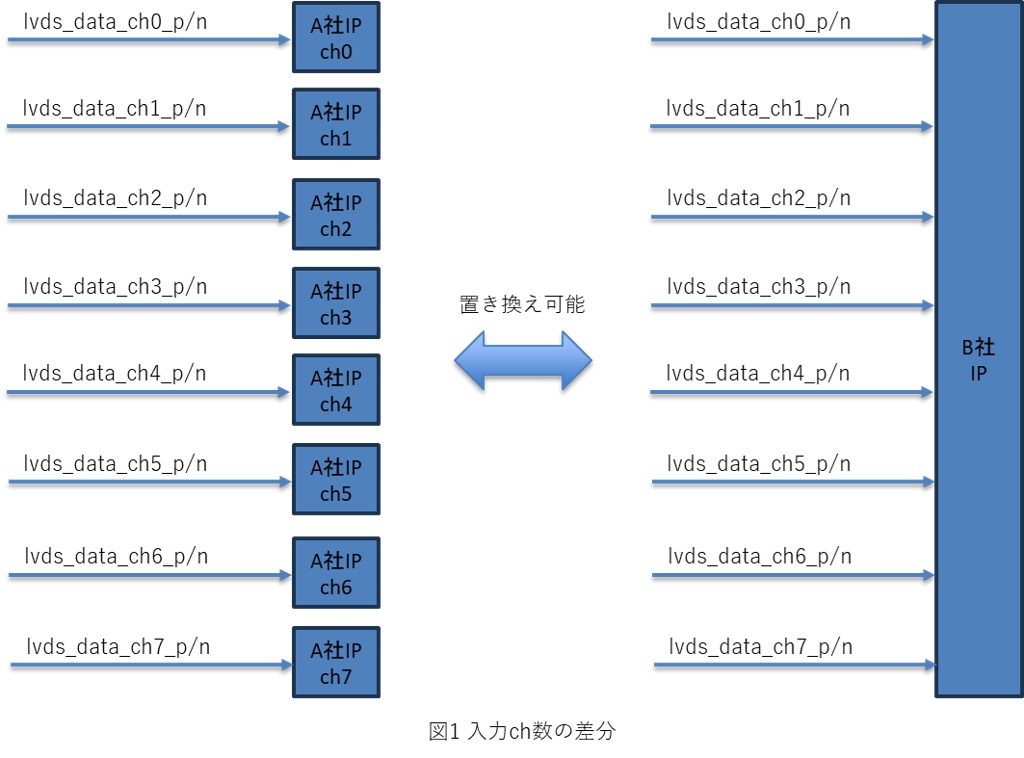

2-2.つまずきポイント①:入力データch数とIPの配置可能数

入力可能なデータch数はメーカーによって差分があります。 1chのみ入力可能なIPもあれば、100ch以上にも対応するIPが存在します。 置き換え後のIPは、置き換え前の入力ch数を満たしているか確認が必要です。

例えばA社IPとB社IPを比較した例を以下の図1に示します。

A社IPでは1chのみが入力可能となっており、B社IPでは多chの入力が可能です。入力可能なデータch数に差分があっても、このようにIPを多数配置可能であれば、置き換えが可能です。 ただしB社IPは1BANKに1つしか配置できないという制約があり、IPの入力可能なch数を超える場合は置き換えができなくなるため、配置個数についてもスペックとして確認が必要です。

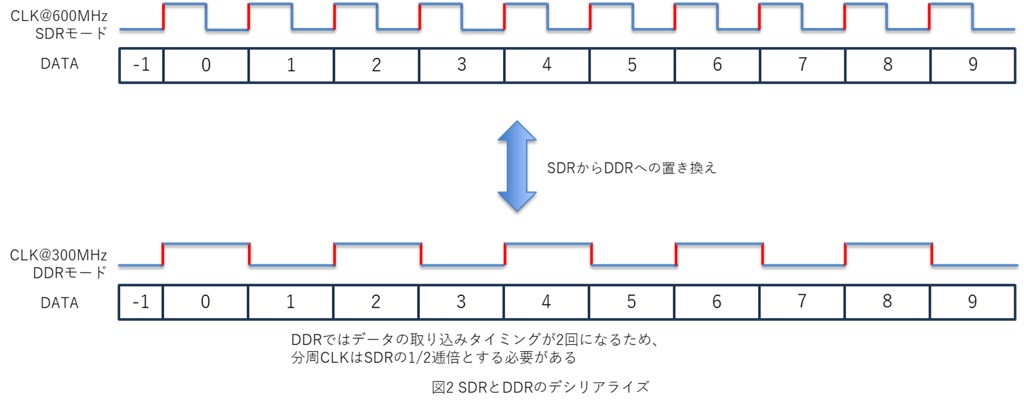

2-3.つまずきポイント②:データレートモードとシリアライズ係数

シリアライズする実効値は、データレートモードとシリアライズ係数を掛け合わせて決定されます。 SDRとDDRどちらに対応しているか、シリアライズ係数はいくつに設定可能となっているか、カタログスペックから比較して確認し、置き換え前後のシリアライズ実効値が一致するか確認が必要です。 データレートモードに違いがあっても、例えば1:10 SDRと1:5 DDRでは、シリアライズ実効値は同じになります。しかしSDRとDDRを置き換える場合、以下の図2で示すように、デシリアライズを行う分周クロックも逓倍させる必要があることに注意が必要です。

2-4.つまずきポイント③:データ遅延量の分解能と最大値

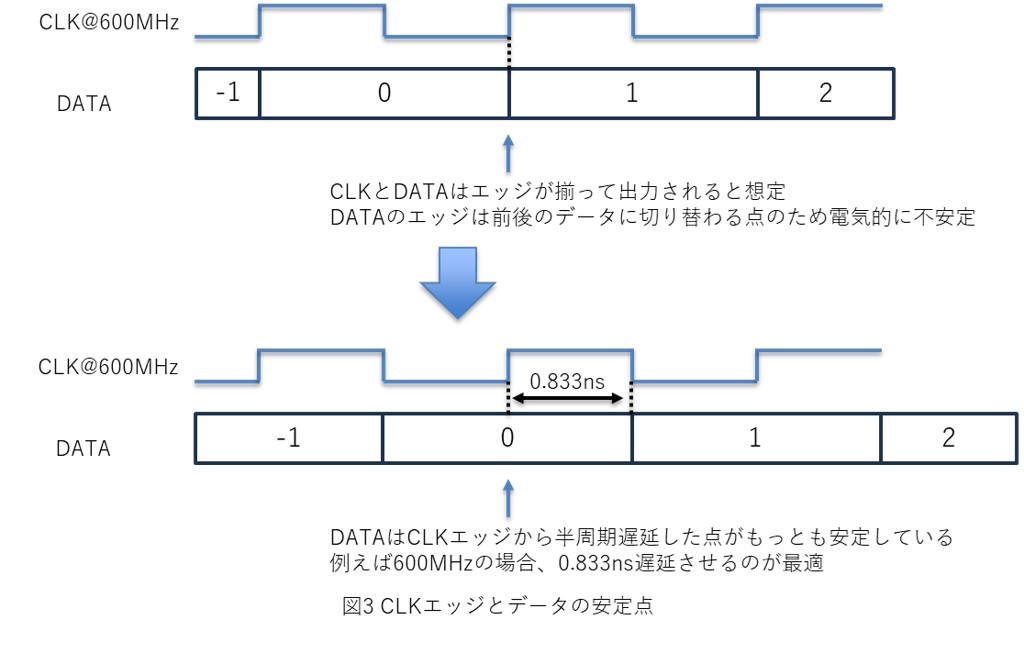

「データ遅延量の分解能と最大値」については、スペックとしてあまり聞きなじみがないと思われます。 入力シリアルデータを安定して取得するためには、図3で示すように、データに遅延を与え、クロックエッジをデータの安定点であるアイパターン(EYE)の中心に当てることが重要となります。

デシリアライザIPにおいては、遅延値は「TAP」と呼ばれるpsオーダーの固定遅延値を複数掛け合わせることで算出されることが多いです(1TAP=72psを最大32TAPまで設定可能、など)。「TAP」の単位が小さいほど安定点に近い遅延値を算出する精度が高まります。また掛け合わせられる数が多いほど、最大遅延量増加し、低データレートに対応が可能です。 データの遅延量はデシリアライザIPとは別に、遅延量調整用IPによって実施されるケースが多いです。そのため、「データ遅延量の分解能と最大値」に関してはデシリアライザIPと合わせて遅延量調整用IPのスペック比較が必要となります。

3.A社IPからB社IPへの置き換え事例紹介

3-1.対象システムの要件

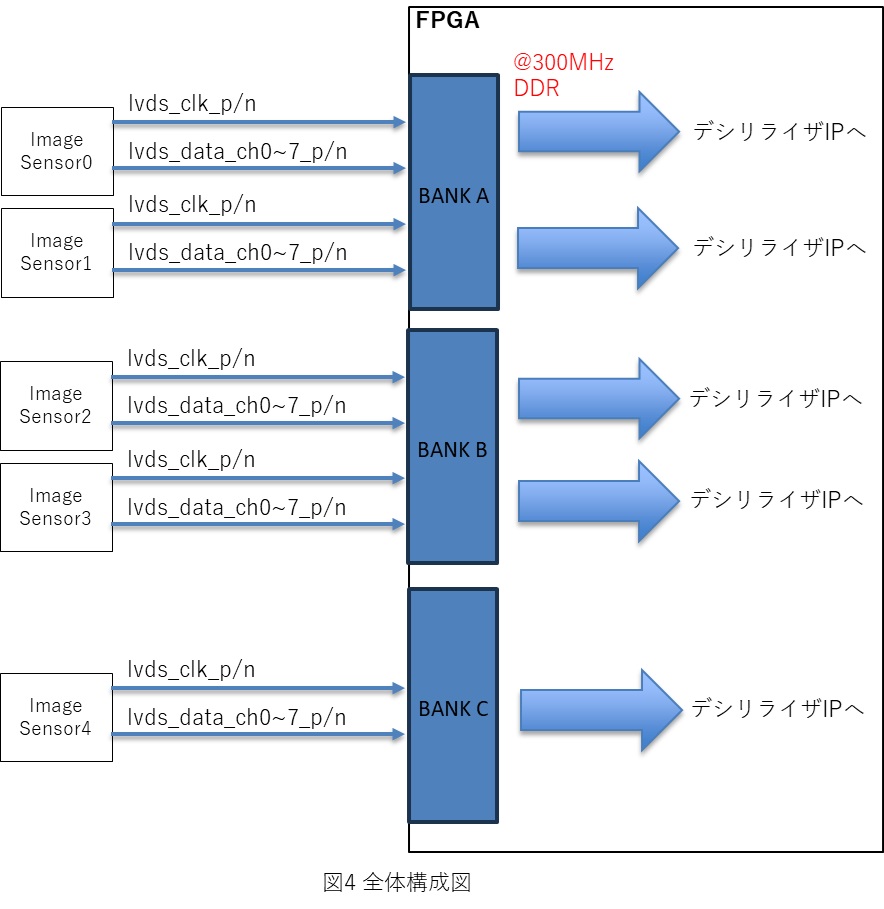

ここからは具体的な置き換え事例として、A社FPGA のデシリアライザIPを用いて SDR 1:8 デシリアライズを行っていた構成を、B社FPGA のデシリアライザIPを用いて 1:4 デシリアライズ構成に置き換えたケースをご紹介します。 まずは対象システムの全体構成図を以下に図示します。

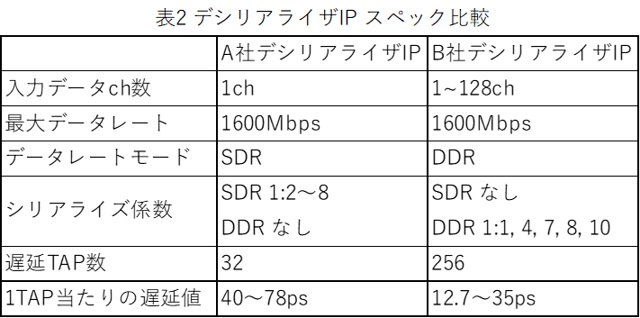

対象システムでは、5個のイメージセンサそれぞれから、8chの差動データペア@600Mbpsが出力されており、FPGA の 3つの BANK へ 2 : 2 : 1 の割合でセンサデータが入力される構成になっています。 次にA社とB社のデシリアライザIPのカタログスペックを比較すると、以下のようになります。

表2の差分を念頭に入れたうえで、各社のデシリアライザIPを使用した構成を紹介していきます。

3-2.A社IP構成のポイント(置き換え前)

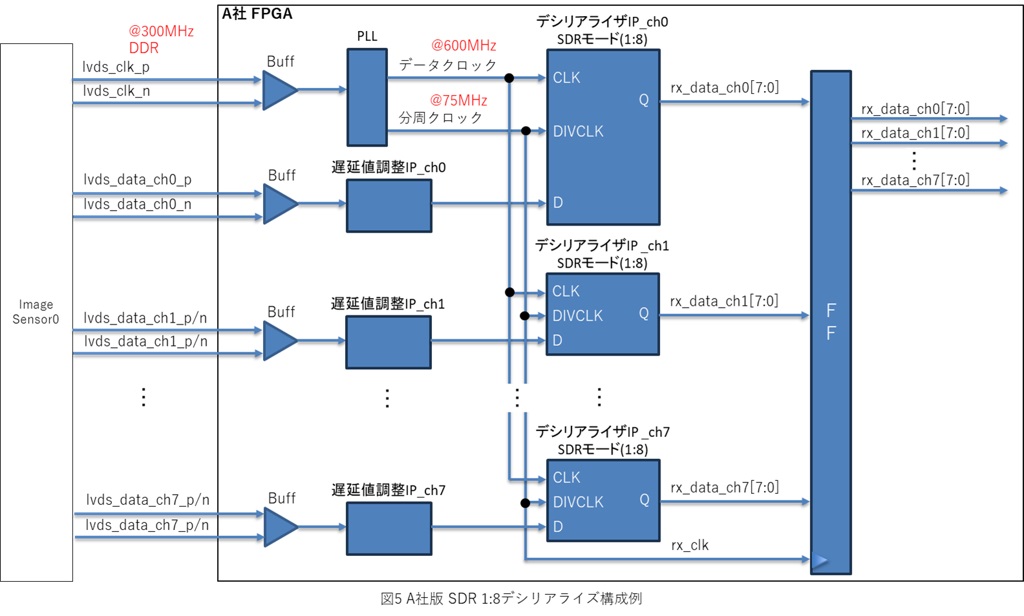

A社IPを使用した際の、デシリアライザブロック内部構成図は以下のようになります。

表2で示したように、A社デシリアライザIPは1chしか入力ができませんが、2-2で示した通り並列配置が可能です。よって図5のように、入力レーン1chにつき1セットのデシリアライザIPを配置しています。 デシリアライズするためにはデータレートと一致したデータクロックと、データを分解するための分周CLKが必要になります。A社デシリアライザIPでは、データクロックと分周クロックはPLL出力を接続する事が推奨されるため、センサクロックは一度PLLを経由後、データクロックと分周クロックを生成して入力しています。 またセンサデータは300MHzのDDRで入力されるのに対し、A社デシリアライザIPはSDRモードで駆動するため、データクロックはPLLを通す際に2逓倍しています。

3-3.B社IP構成のポイント(置き換え後)

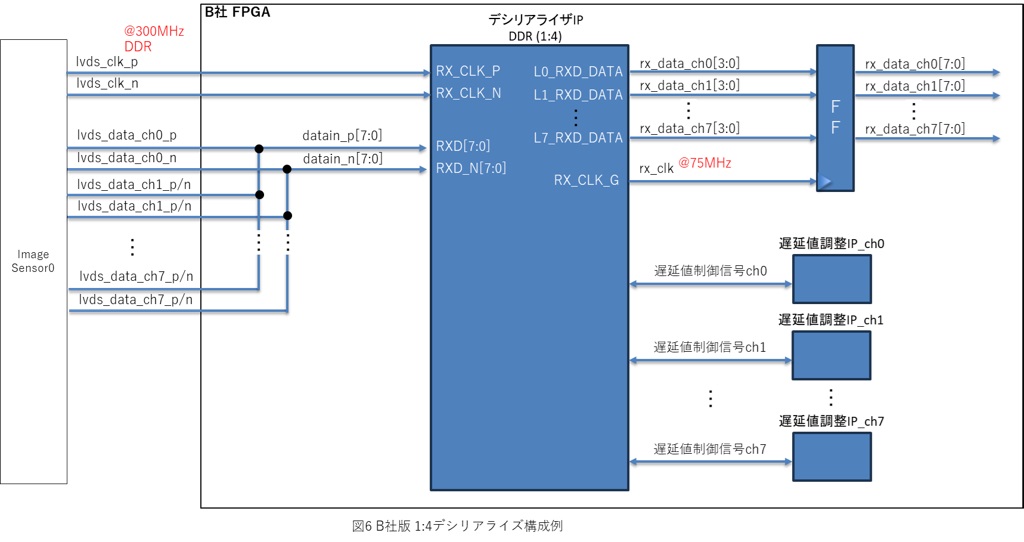

次にA社IP構成を、B社IPを使用した構成に置き換えたものを以下に図示します。

表1で示した通り、B社IPは1個のIPで8chのデータを取得可能です。よって図6のように、デシリアライザIPは並列配置せず、1つで8chのデータを取り込んでいます。 ただし遅延値調整IPは1chにつき1つ必要となる仕様のため、A社IPと同じく8ch分の並列配置を行っています。 またA社構成ではIP外でデータクロックと分周クロックを用意する必要がありましたが、B社IPでは内部にPLL/Dividerを搭載しているため、外部のPLLで各CLKを生成する必要がありません。差動バッファについても同じく内蔵されているため、入力CLK/データはそのまま接続している差分があります。 分周CLKもIPから出力されるため、後段回路はIPから出力されたCLKで同期可能です。DividerまたはPLLどちらを使用するかはIPのモード設定によって変更可能です。

今回の構成ではSDR 1:8を DDR 1:4に変更しているため、分周CLKの1CLK当たりの出力bit数に差分が生じます。SDRとDDRの差はデータクロックの2逓倍によって吸収されますが、シリアライズ係数の違いは後段回路によって補填する必要があります。今回の場合、1CLK当たりの出力bit数がA社IPでは8bit、B社IPでは4bitとなるため、B社IPの後段回路で2clk分のデータを貯めれば、同様のデシリアライズが実現可能です。

3-4.遅延値の分解能をスペックから算出する事例紹介

表2のスペック比較表から遅延値の分解能についても差分がある事が分かります。 最後にスペック比較表から遅延値の分解能を算出する例を以下に示したいと思います。

A社FPGA 最大32TAPが設定可能とあり、その単位は40~78psとなっています。 よって設定可能な遅延値は40~2496psとなり、約400MHzまでのデータを1周期分遅延させることが可能と見ることができます。

B社FPGA 最大256TAPが設定可能とあり、その単位は12.7~35psとなっています。 よって設定可能な遅延値は12.7~8960psとなり、約115MHzまでのデータを1周期分遅延させることが可能と見ることができます。

分解能スペックを比較 最小単位・最大遅延値ともにB社IPの方が幅広いため、A社IP→B社IPへの置き換えへには支障は生じません。しかし逆にB社IP→A社IPへの置き換えの場合は、精度が荒くなるため、データの安定点を十分に狙えず、データの安定点を取得できない可能性がある、と判断できます。

また「1TAP当たりの遅延値」については、CLK周波数やIPのモード設定、FPGA種によって振り幅があるため、単純なカタログスペックのMin/Maxだけでなく、どのような条件で設定可能なスペックであるか確認するようにしましょう。

まとめ

本稿ではデシリアライズIPを使った構成の置き換えに関して、検討ポイントと実例構成をご紹介しました。 FPGA設計開発ではコストやサイズ、EOL(End of Life)の観点からFPGAの変更を検討する場面も少なくありません。その際、特定のIPを前提とした回路を、置き換え先でもどこまで再現できるかは、非常に重要な検討内容となります。

ミラクシアでは、FPGA ベンダ内外を問わず、こうした置き換え検討からアーキテクチャ設計、実装・検証まで一貫して支援しています。FPGA 置き換えや高速インターフェース周りでお困りの点があれば、ぜひお気軽にご相談ください。

採用情報

ミラクシアでは一緒に組込みソフト開発をする仲間を募集しています。